# ON SIMPLIFYING AND OPTIMIZING PROGRAMS FOR HETEROGENEOUS COMPUTING SYSTEMS

dissertation

by

## IVAN GRASSO

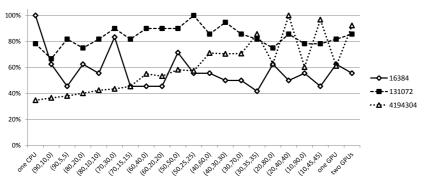

submitted to the Faculty of Mathematics, Computer Science and Physics of the University of Innsbruck

> in partial fulfillment of the requirements for the degree of doctor of philosophy

*advisor*: Prof. Dr. Thomas Fahringer, Institute of Computer Science second advisor: Prof. Dr. Sabine Schindler, Institute of Astro and Particle Physics

Innsbruck, March 19, 2017

I certify that the work in this thesis has not previously been submitted for a degree nor has it been submitted as part of requirements for a degree except as fully acknowledged within the text.

I also certify that the thesis has been written by me. Any help that I have received in my research work and the preparation of the thesis itself has been acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis.

Ivan Grasso, Innsbruck, March 19, 2017

We have seen that computer programming is an art, because it applies accumulated knowledge to the world, because it requires skill and ingenuity, and especially because it produces objects of beauty.

- Donald E. Knuth

## ACKNOWLEDGEMENTS

First and foremost, I would like to express gratitude to my academic adviser Prof. Thomas Fahringer for his guidance and support. He gave me the freedom to follow my own ideas while steering me in the right direction when necessary. I would also like to thank my second adviser Prof. Sabine Schindler as well as the thesis committee and the external reviewers.

I would further like to thank my friends and colleagues from the DPS Group. In particular, a special thank goes to Simone Pellegrini, Klaus Kofler, and Biagio Cosenza. This thesis would have never been possible without their help.

Furthermore, I would like to thank Alex Ramirez and the Heterogeneous Architectures group for the great experience during my internship at the Barcelona Supercomputing Center.

I would like to thank the funding bodies which enabled this work to be conducted: the FWF Austrian Science Fund, the FWF Doctoral School Computational Interdisciplinary Modelling (DK CIM) and the Mont-Blanc FP7 European Project.

I wish to thank my family for the unconditional encouragement throughout the course of my life. In particular, I owe my accomplishments to my parents who always supported my interest in computer science.

Last but not least, I would like to thank Birgit who has always been there for me.

Today, with the growth of highly parallel and heterogeneous architectures, systems composed of a combination of multicore CPUs, GPUs, and accelerators are becoming more common in HPC. Although heterogeneous architectures bring considerable benefits from a performance and energy perspective, they also make application development very challenging introducing the necessity of different parallel programming paradigms. Recently, in order to fully harvest the computational capabilities of such architectures, researchers focused their attention on software development tools to simplify the daunting programming task. In a similar line of investigation, this dissertation tackles the optimization and simplification of programs for heterogeneous computing systems. In the context of low-power architectures, we analyze the performance and energy advantages of embedded GPUs showing the benefits of this architecture for HPC workloads. In order to maximize the performance of heterogeneous compute nodes, we investigate a new compiler/runtime approach to generate programs that concurrently use all the heterogeneous resources and we propose two low-complexity heuristics addressing the problem of scheduling independent tasks. Finally, to simplify the development of heterogeneous distributed applications, we present libWater, a library-based extension of the OpenCL programming model that, with a simple interface, abstracts the underlying distributed architecture without losing control over performance.

# CONTENTS

| 1                  | INTRODUCTION                                           |                                 |                                       | 1  |  |  |

|--------------------|--------------------------------------------------------|---------------------------------|---------------------------------------|----|--|--|

|                    | 1.1 Motivation                                         |                                 |                                       | 1  |  |  |

|                    | 1.2                                                    | State of Art                    |                                       |    |  |  |

|                    | 1.3                                                    | oals and Organization           | 3                                     |    |  |  |

| 2                  | MODEL                                                  |                                 |                                       |    |  |  |

| 2.1 Hardware Model |                                                        |                                 |                                       | 5  |  |  |

|                    | 2.2                                                    | Software Model                  |                                       |    |  |  |

|                    | 2.3                                                    |                                 |                                       |    |  |  |

|                    |                                                        | 2.3.1 P                         | latform Model                         | 19 |  |  |

|                    |                                                        | 2.3.2 E                         | xecution Model                        | 20 |  |  |

|                    |                                                        | 2.3.3 N                         | ſemory Model                          | 21 |  |  |

|                    |                                                        | 2.3.4 P                         | rogramming Model                      | 23 |  |  |

|                    | 2.4 The Message Passing Model                          |                                 |                                       |    |  |  |

|                    |                                                        | 2.4.1 P                         | oint-to-Point Communication Model     | 24 |  |  |

|                    |                                                        | 2.4.2 C                         | Collective Communication Model        | 25 |  |  |

| 3                  | ENERGY EFFICIENT HPC ON EMBEDDED SOCS                  |                                 |                                       |    |  |  |

|                    | 3.1                                                    | Introduction                    |                                       |    |  |  |

|                    | 3.2                                                    | Related Work                    |                                       |    |  |  |

|                    | 3.3                                                    | ARM Mali T-604 GPU Architecture |                                       |    |  |  |

|                    |                                                        | 3.3.1 C                         | penCL Optimizations for Mali GPU      | 30 |  |  |

|                    | 3.4                                                    | 3.4 Evaluation                  |                                       |    |  |  |

|                    |                                                        | 3.4.1 P                         | erformance Analysis                   | 38 |  |  |

|                    |                                                        | 3.4.2 P                         | ower Analysis                         | 41 |  |  |

|                    |                                                        | 3.4.3 E                         | nergy-to-Solution Analysis            | 43 |  |  |

|                    | 3.5                                                    | Summar                          | y                                     | 44 |  |  |

| 4                  | SCHEDULING TECHNIQUES FOR HETEROGENEOUS NODES          |                                 |                                       |    |  |  |

|                    | 4.1 Automatic Task Partitioning on Heterogeneous Nodes |                                 |                                       |    |  |  |

|                    |                                                        | 4.1.1 R                         | elated Work                           | 48 |  |  |

|                    |                                                        | 4.1.2 T                         | he Insieme Compiler-Runtime Framework | 50 |  |  |

|                    |                                                        | 4.1.3 E                         | xperimental Environment               | 53 |  |  |

|                    |                                                        |                                 | valuation                             | 57 |  |  |

|                    | 4.2                                                    | Tensor C                        | Computation on Heterogeneous Nodes    | 61 |  |  |

|                    |                                                        | 4.2.1 R                         | elated Work                           | 62 |  |  |

|    |                                         | 4.2.2                                     | Tensor Computation               | 63  |  |  |  |

|----|-----------------------------------------|-------------------------------------------|----------------------------------|-----|--|--|--|

|    |                                         | 4.2.3                                     | Scheduling Independent Fragments | 66  |  |  |  |

|    |                                         | 4.2.4                                     | Experimental Environment         | 67  |  |  |  |

|    |                                         | 4.2.5                                     | Evaluation                       | 69  |  |  |  |

|    | 4.3                                     | Summ                                      | nary                             | 73  |  |  |  |

| 5  | SIMPLIFYING THE PROGRAMMING OF CLUSTERS |                                           |                                  |     |  |  |  |

|    | 5.1                                     | Introduction                              |                                  |     |  |  |  |

|    | 5.2                                     | Related Work                              |                                  |     |  |  |  |

|    | 5.3                                     | The libWater Programming Interface        |                                  |     |  |  |  |

|    | 5.4                                     | The libWater Distributed Runtime System 8 |                                  |     |  |  |  |

|    |                                         | 5.4.1                                     | Runtime System Optimizations     | 89  |  |  |  |

|    | 5.5                                     | Evalua                                    | ation                            | 94  |  |  |  |

|    |                                         | 5.5.1                                     | VSC2 CPU Cluster                 | 96  |  |  |  |

|    |                                         | 5.5.2                                     | MinoTauro GPU Cluster            | 101 |  |  |  |

|    |                                         | 5.5.3                                     | Ortler Mixed-node Cluster        | 101 |  |  |  |

|    | 5.6                                     | Summ                                      | nary                             | 104 |  |  |  |

| 6  | CONCLUSION AND FUTURE WORK              |                                           |                                  |     |  |  |  |

|    | 6.1                                     | Contr                                     | ibutions                         | 106 |  |  |  |

|    | 6.2                                     | 2 Future Work                             |                                  |     |  |  |  |

| вт | BLIO                                    | GRAPH                                     | ſΥ                               | 115 |  |  |  |

| ~1 | 0                                       |                                           | -                                |     |  |  |  |

#### 1.1 MOTIVATION

High Performance Computing (HPC) has been traditionally restricted to important scientific challenges and few industrial domains where investments were large enough to support the massive infrastructure costs. However, nowadays HPC has been recognized as a powerful means to increase the competitiveness of countries through the development of their public and private sectors. Meaningful scientific discoveries have been achieved using HPC and the range of disciplines that depend on it is continuously growing [48]. The current roadmap for HPC aims at building computing systems capable of one exaflops (10<sup>18</sup> floating point operations per second) by 2021 [35]. Going toward exascale, the current levels of power demand cannot be met for cost and heat dissipation reasons. These constraints have led to the introduction of supercomputers which take into account not only performance but also power consumption. The Green500 list ranks the top 500 supercomputers in the world by energy efficiency using the widely accepted metric FLOPS-per-Watt [107]. Overall, heterogeneous systems demonstrate better energy efficiency than homogeneous systems and the current list is dominated by GPU Clusters based on NVIDIA P100 Tesla GPUs [115]. Although GPUs offer a clear advantage in terms of energy efficiency, recently also other technologies are emerging. Striking examples are the Japanese effort towards building supercomputers based on embedded ARM processors [118] and the new Intel massively-parallel multicore processor Knights Landing [55]. The uncertainty regarding which architecture will be dominant in the coming years poses an additional challenge further complicating the already difficult task of designing HPC applications. Nowadays, to efficiently access different hardware resources and levels of parallelism, developers are required to combine multiple languages and programming paradigms. Therefore, the availability of automatic tools to mitigate the complexity of software

and increase its portability across different hardware platforms has become of paramount importance.

#### 1.2 STATE OF ART

Several paradigms and frameworks have been proposed in the literature for programming parallel heterogeneous architectures. This section will give an overview of the most successful models while the related work for each area of contribution will be discussed in more detail within their respective chapters.

Nowadays the main approaches used to program heterogeneous hardware fall in two categories: explicit programming models and directive-based models.

**Explicit Programming Models.** Explicit models give the developer complete control over the hardware resources to create very efficient and optimized code. The most renowned explicit programming models are CUDA and OpenCL.

*CUDA* [86] is a parallel computing model created by NVIDIA. It allows software developers to use CUDA-enabled GPUs for general-purpose processing. The CUDA platform is a software layer, designed to work with programming languages such as C, C++, and Fortran, that gives direct access to the GPU's virtual instruction set and parallel computational elements.

*OpenCL* [60] is an open standard for programming parallel heterogeneous architectures maintained by the Khronos Group consortium. It provides an interface for writing programs that execute across heterogeneous platforms as central processing units (CPUs), graphics processing units (GPUs), digital signal processors (DSPs), fieldprogrammable gate arrays (FPGAs), and other hardware accelerators.

**Directive-based Models.** Programming with explicit models is often a difficult task, especially for non-computing specialists. An alternative is represented by directive-based models that allow developers to mark regions of code for parallel acceleration with a minimum amount of effort. OpenMP and OpenACC are the most representative models of this category.

*OpenMP* [89] is an API consisting of compiler directives and library routines for high-level parallelism in C, C++, and Fortran programs.

Starting with OpenMP 4.0, it is possible to offload parallel regions to different devices, such as GPUs or accelerators. The OpenMP directives are platform independent, allowing a high degree of portability and performance with little programming effort.

*OpenACC* [88] provides a collection of compiler directives to specify loops and regions of code in standard C, C++, and Fortran to be offloaded from a host CPU to an attached GPU or accelerator. The OpenACC directives allow programmers to create high-level host/device programs without the need to explicitly initialize the devices or manage data transfers. All of these details are implicit in the programming model and are managed by the OpenACC compilers and runtimes.

Recently, *SYCL* [62], a new abstraction layer that builds on the concepts of portability and efficiency, was introduced. SYCL is a royalty-free, cross-platform layer that enables code for heterogeneous processors to be written in a single-source style using standard C++. Template functions can contain both host and device code to construct complex algorithms that use OpenCL acceleration.

#### 1.3 THESIS GOALS AND ORGANIZATION

This thesis will focus on OpenCL that currently offers a clear advantage in terms of number of accessible devices and level of hardware control. Using the OpenCL programming model, we will explore and discuss novel approaches aiming at both simplifying and optimizing programs for heterogeneous computing systems. This thesis is divided into five additional chapters as follows:

**Chapter 2** introduces the models that describe all the abstractions used in this work.

**Chapter 3** focuses on embedded systems analyzing the performance and energy advantages of embedded GPUs for HPC. We identify, implement and evaluate software optimization techniques for efficient utilization of the ARM Mali GPU Compute Architecture showing for the first time that embedded GPUs have qualities that make them good candidates for HPC systems.

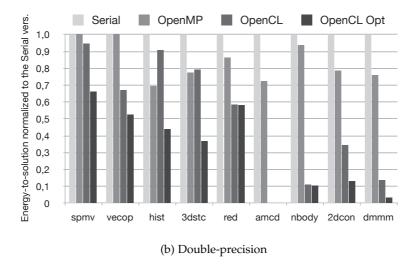

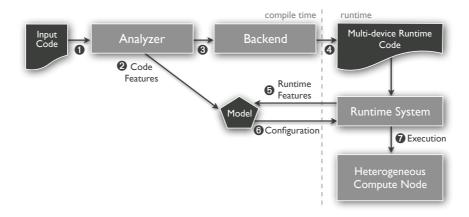

**Chapter 4** investigates the distribution of tasks among the available devices in order to maximize the performance of heterogeneous com-

pute nodes. Based on a powerful compiler/runtime infrastructure, we develop a new approach for converting a single-device OpenCL program to a multi-device OpenCL program able to concurrently take advantage of all the heterogeneous resources.

We also propose and implement two low-complexity heuristics addressing the problem of scheduling independent tasks in heterogeneous compute nodes.

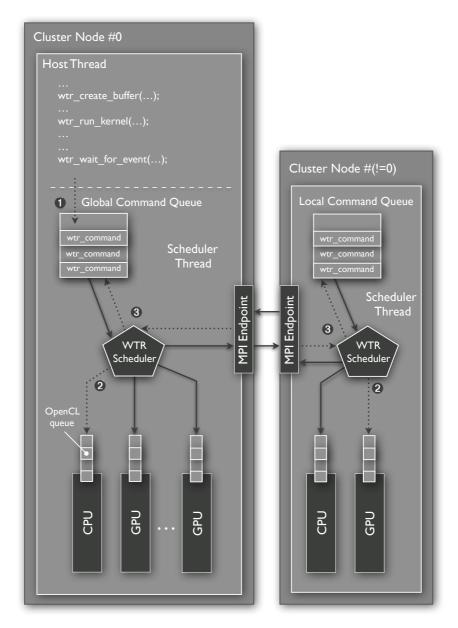

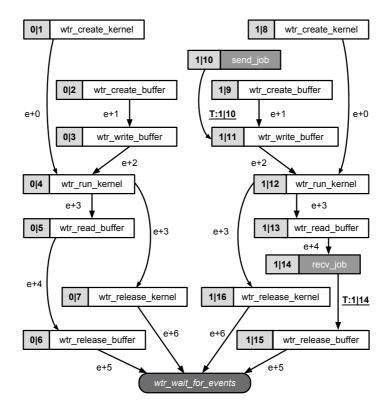

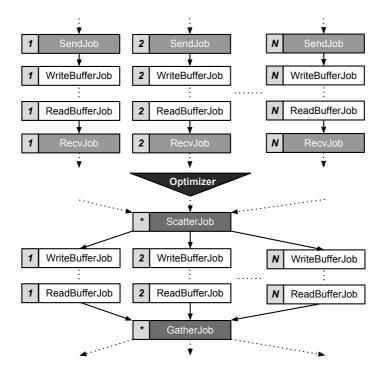

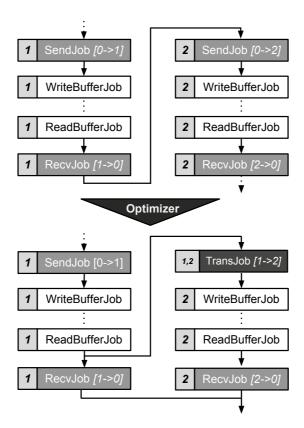

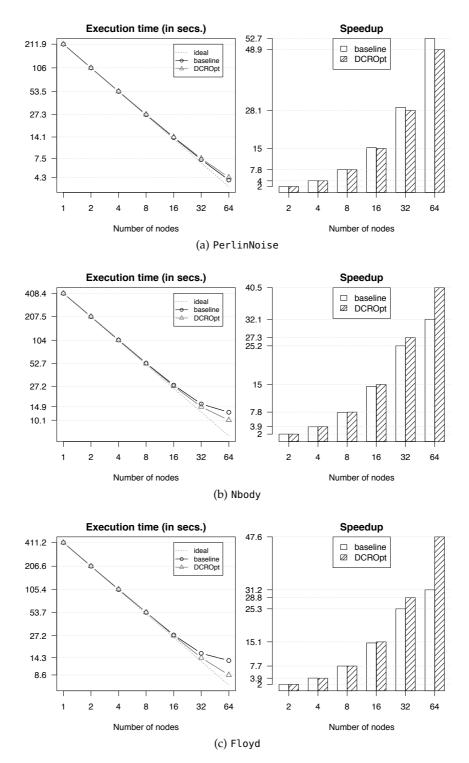

**Chapter 5** introduces *libWater*, an extension of the OpenCL programming model that simplifies the development of heterogeneous distributed applications. libWater consists of a simple interface, which is a transparent abstraction of the underlying distributed architecture. It provides a runtime system which tracks dependency information enforced by event synchronization to dynamically build a DAG of commands, on which we automatically apply optimizations.

**Chapter 6** concludes the thesis discussing future work and providing the list of peer-reviewed publications which support our findings.

#### MODEL

In this chapter we introduce the models that describe all the abstractions used in the thesis. In Section 2.1, starting from basic concepts we formally describe the structure of the hardware architectures addressed by the analyses and optimizations. The software model, presented in Section 2.2, introduces the terminology for program and parallelism. In Section 2.3, we describe the concepts and the architecture of the Open Computing Language model. Finally, in Section 2.4, we present the message passing model.

#### 2.1 HARDWARE MODEL

In this section, using a bottom-up approach, we introduce and define the concepts that describe the hardware which is utilized in this thesis. The hardware is represented through a formal model composed of entities and relations.

Let E denote an entity set and let us define a basic entity  $e \in E$  to be a hardware item which can be distinctly identified. Let us define  $r \in R \subseteq E \times E$  as a binary relation on E that enables the transfer of data between two entities. Then a complex entity c = (E, R) consists of a non-empty set E of basic or complex entities, and a set  $R \subseteq E \times E$ of relations. Relations can also be expressed in a more compact form  $(e_i, e_j), (e_j, e_k) \in R \equiv \langle e_i, e_j, e_k \rangle \in R$ . This form defines a sequence of connected entities and is useful to represent how data moves between the different entities. Entities and relations can also feature attributes that describe their elementary properties. An attribute :  $E \vee R \rightarrow V$ can be formally defined as a function which maps an entity set or relation set into a value set V, also known as the domain of the attribute. Definition 2.1 (Latency and Bandwidth)

$\forall \mathbf{r} = (e_j, e_k) \in \mathbb{R} \ \exists \ latency : \mathbb{R} \to \mathbb{R}, \ \exists \ bandwidth : \mathbb{R} \to \mathbb{N}$ The attribute *latency* of a relation  $\mathbf{r}$  is defined as the time, in seconds, required to transfer a minimal amount of data between  $e_j$  and  $e_k$ . Similarly, the attribute *bandwidth* is defined as the amount of data that can be transferred from  $e_j$  to  $e_k$  per second.

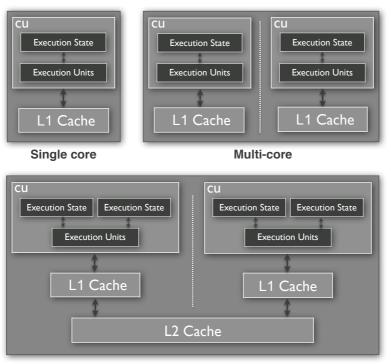

#### **Definition 2.2** (Computing Unit)

$\forall cu = (E, R) \in CU \exists es, eu \in E \mid (es, eu) \in R$

A *computing unit*, cu, is defined as a complex entity that performs arithmetic, logical, and control operations. Such an entity is composed of an *execution state*, es, and one or more *execution units*, eu.

The *execution state* comprises general purpose and interrupt controller registers, while an *execution unit* comprises the resources for the instruction execution. The execution unit also features an attribute *width* that denotes the size of the data that can be processed in a single step of execution. In some cases, to better utilize the resources, a computing unit contains duplicated execution states that share the same execution units. This technique is known as simultaneous multi-threading (SMT) and is used to make a single computing unit appear as multiple logical computing units.

#### **Definition 2.3** (Memory Unit)

A *memory unit*,  $mu \in MU$ , is defined as a basic entity capable of temporarily storing user or system data. Such an entity holds a relation with the entities which can access its content (i.e., computing units or memory units) and features an attribute *size* that expresses the total amount of memory available in bytes.

Particular memory units are *cache* and *local memory*. A *cache*,  $L_n$ , is defined as a small and low-latency memory unit whose content is automatically managed in hardware. Caches are usually organized in hierarchies of memory units and feature an attribute level  $n : MU \rightarrow \mathbb{N}$  that denotes their position in the hierarchy. A cache in a lower level (e.g.,  $L_1$ ) contains only a subset of the data present in a higher level cache (e.g.,  $L_2$ ). Caches that share common data need to be synchronized to offer a coherent view of their content. This difficulty, generally known as *cache coherence problem*, is usually solved in hardware

with the use of a protocol that tracks the state of all the shared data. In addition to the *size* and *level*, a cache entity features the following attributes:

- *associativity* denotes the number of cache locations in which a memory entry can be mapped.

- *replacement policy* represents the heuristic utilized to choose the cache entry to evict in order to make room for a new entry.

A *local memory*, LM, is defined as a small and low-latency memory unit that can be directly addressed by the programmer. The local memory does not operate like a cache since it is neither transparent to the software nor does it contain hardware structures able to predict the data to load. For these reasons, it consumes relatively little power compared with hardware-managed caches but also introduces new challenges for the programmer that needs to explicitly maintain the data consistency.

#### **Definition 2.4** (Processor)

$\forall$  CPU = (E, R)  $\exists$  cu, L<sub>1</sub>, ..., L<sub>n</sub>  $\in$  E |  $\langle$  cu, L<sub>1</sub>, ..., L<sub>n-1</sub>, L<sub>n</sub> $\rangle \in$  R A *processor*, CPU, represents the core component of a computing system and is defined as a complex entity consisting of one or more computing units connected with one or more levels of cache.

The processor is designed to provide good performance during the execution of the operating system and the broad range of user applications. As depicted in Figure 2.1, based on the number of computing units and shared resources, a processor is named differently:

- *single core* a processor with a single computing unit and one or more levels of cache.

- *multi-core* a processor with two or more computing units and one or more levels of cache.

- *multi-core with SMT* a multicore processor with simultaneous multi-threading.

A processor entity features the following attributes:

• *number of cores* - denotes the number of computing units with related L1 caches.

Multi-core with SMT

Figure 2.1: Hardware model for different types of processors

• *clock frequency* - the maximum frequency at which the processor can run.

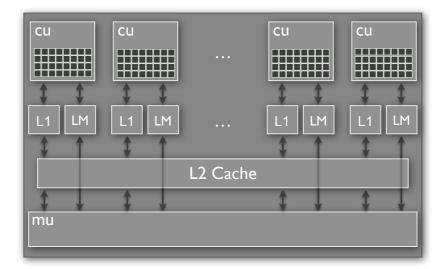

**Definition 2.5** (Graphics Processing Unit)  $\forall$  GPU = (E, R)  $\exists$  cu, L<sub>1</sub>, L<sub>2</sub>, LM, mu  $\in$  E |

$\langle cu, L_1, L_2, mu \rangle, \langle cu, LM, mu \rangle \in R$

A *graphics processing unit*, GPU, is defined as a complex entity able to perform highly parallel operations on data. Such an entity consists of a large memory unit and multiple computing units connected with multiple cache levels and local memories.

GPUs have evolved from special-purpose entities purely used for graphics processing to programmable entities that can execute a wide range of applications. As depicted in Figure 2.2, each computing unit of a GPU contains a large number of execution units that, combined together, offer high theoretical peak performance. To absorb the memory request of the computing units, the GPU entity takes advantage of a memory hierarchy and a high bandwidth memory unit. The bandwidth attribute of the relation between the memory unit and

Figure 2.2: Hardware model for the GPU entity

the caches/local memories is in the order of hundreds of GB/s. A GPU entity features the following attributes:

- *number of computing units* denotes the number of computing units.

- *clock frequency* expresses the maximum frequency at which the computing units can run.

- *memory size* denotes the total amount of GPU memory available in bytes.

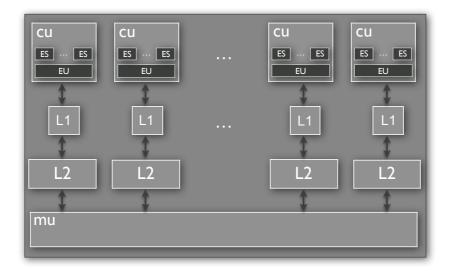

## Definition 2.6 (Accelerator)

$\forall \ ACL = (E,R) \ \exists \ cu, L_1, L_2, mu \in E \ | \ \langle cu, L_1, L_2, mu \rangle \in R$

An *accelerator*, ACL, is defined as a complex entity able to accelerate highly parallel computing workloads. Such an entity consists of a large memory unit and many computing units connected with multiple cache levels.

As depicted in Figure 2.3, the accelerator hardware model resembles the CPU hardware model. Modern accelerators (e.g., Intel Xeon Phi) are based on a many-core architecture that consists of a large number of computing units with simultaneous multi-threading running at a low clock frequency. Similar to a GPU entity, an accelerator is composed of a cache hierarchy, a high bandwidth memory unit and

Figure 2.3: Hardware model for the accelerator entity

supports the same entity attributes.

## Definition 2.7 (Secondary Storage)

A *secondary storage* or *disc storage*, *ss*, is defined as a basic entity that is capable of permanently storing user or system data.

## Definition 2.8 (Network Interface)

A *network interface*, ni, is defined as a basic entity used to physically interface a compute node with other compute nodes or network-attached secondary storages.

Different network interfaces offer different performance characteristics. Usually, a relation between network interfaces based on highspeed interconnects, like Infiniband EDR, has an attribute bandwidth of around 100 Gbps and an attribute latency of 130 ns. A relation based on more affordable interconnects, such as Ethernet, has an attribute bandwidth of 10 Gbps and an attribute latency of 2 to 4  $\mu$ s.

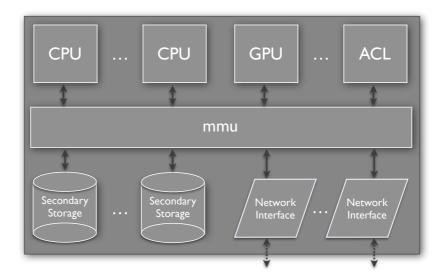

Figure 2.4: Hardware model for the compute node entity

#### Definition 2.9 (Compute node)

$\forall \ cn = (E, R) \in CN \ \exists \ CPU, GPU, ACL, ss, ni, mmu \in E \mid$

$\forall e \in E \mid e \neq mmu \exists (e, mmu) \in R$

A *compute node* is defined as a complex entity representing a computing system (e.g., desktop, server). As depicted in Figure 2.4, such an entity can consist of multiple CPUs, GPUs, accelerators, secondary storages and network interfaces, all connected with the same *main memory unit*, mmu.

Based on the entities that compose a compute node, it can be defined as:

- *homogeneous* a node with one or more CPUs but without GPUs or accelerators.

- *heterogeneous* a node with one or more CPUs and one or more GPUs or accelerators.

GPUs and accelerators are external devices that need to be connected through PCI Express expansion slots. Any data requested from such entities needs to be copied from the compute node memory(mmu) to the entity memory and back before being accessible by the CPU entity. Due to the current bandwidth limitation of the PCI Express (8-16 GB/s), these memory transfers can lead to significant overhead during the transmission of data increasing the overall workload processing time.

Figure 2.5: Different types of clusters

## **Definition 2.10** (Cluster)

A *cluster* or *distributed memory system* is defined as a complex entity composed of a set of locally connected compute nodes.

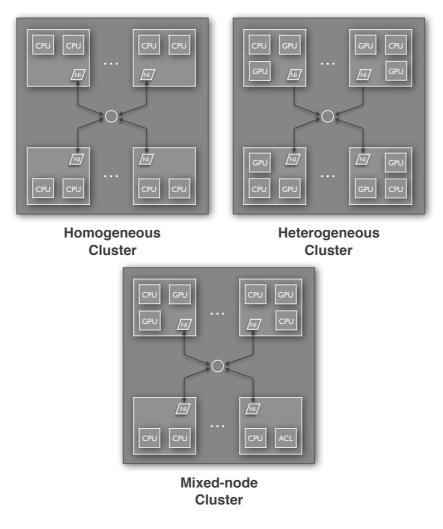

As depicted in Figure 2.5, based on the type of compute nodes that compose a cluster, it can be defined as:

- *homogeneous* composed of homogeneous compute nodes.

- *heterogeneous* composed of heterogeneous compute nodes.

- *mixed-node* composed of compute nodes of different types.

Figure 2.6: Hardware model for the SoC entity

## Definition 2.11 (System on Chip)

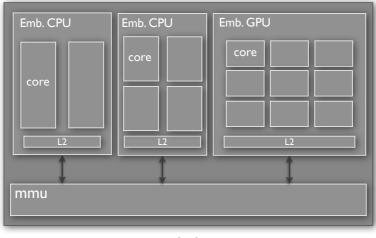

A *system on chip*, SoC, is defined as a complex entity composed of embedded CPUs, embedded GPUs and memory units, packed together into a single chip.

Differently from CPUs and GPUs present in compute nodes, the embedded versions present in SoCs need to be designed taking into account more strict power and space constraints. As depicted in Figure 2.6, to save space, embedded GPUs do not have a GPU memory unit, but share the main memory unit with the other entities present in the chip. Modern SoCs often also provide a big.LITTLE hardware configuration [40] with multiple CPUs that feature different performance and power characteristics. In such case, to reduce the overall power consumption of the chip, the operating system can choose to activate or deactivate the different CPUs depending on the applications workload.

#### 2.2 SOFTWARE MODEL

As mentioned in the previous section, a compute node is composed of a variety of different hardware entities (i.e., memories, processors). Application programs do not directly access the hardware but use the abstract set of resources that the operating system provides. The operating system accesses and manages the hardware controlling the allocation of entities among the various programs that request them.

**Definition 2.12** (Program)

A *program*, r = (M, V), is defined as a sequence of *statements* M, and a *program state* V.

A *variable* is defined as a storage location, with a specific *data type* and an associated *identifier*, which contains some quantity of information referred to as *value*. The attribute data type determines the set of values that can be stored in a variable and the set of operations that can be executed on it. A *program state* is defined, at any given point in the program's execution, as the content of all the variables  $v \in V$ .

A *statement*,  $m \in M$ , represents the basic element of a program and describes the computation by altering the values stored in the variables  $v \in V$ . Statements are generally executed in sequence from top to bottom, however, the program may contain control flow statements that alter the *flow of execution* (e.g., if, switch, for statements). To facilitate the readability of a program, statements are often grouped together in functions that perform specific tasks.

A *function* is commonly defined as

*name*  $(v_0, ..., v_n) \rightarrow type \{m_0, ..., m_m\}$

where

- *name* denotes the identifier by which the function can be called.

- $v_0, ..., v_n$  is an ordered list of variables, called *parameters*, that are initialized with the corresponding arguments passed in the function call.

- *type* expresses the type of the value returned by the function.

- m<sub>0</sub>, ..., m<sub>m</sub> represents the block of statements executed by the function.

Every program contains a *main function* which designates the starting point of the flow of execution.

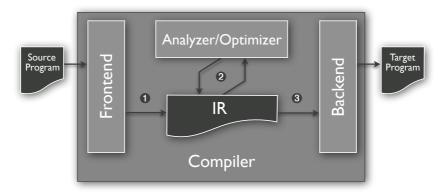

## Definition 2.13 (Compiler)

A *compiler* is a program capable of translating a *source program* into a semantically equivalent *target program*.

Figure 2.7: Compiler software model

As depicted in Figure 2.7, a compiler is composed of a frontend, an analyzer/optimizer, and a backend. In step **0**, the frontend translates the input code into an internal *intermediate representation* of the source program, called IR. An important task of the frontend is to collect and provide information regarding the syntactic and semantic errors encountered during the translation phase, so that the user can take corrective actions in the source program. In step **2**, the analyzer applies control-flow and data-flow analysis [2] on the IR to collect useful information. The optimizer, based on the results of the analysis, applies some transformations with the purpose of optimizing the representation and improving the quality of the generated code. Finally, in step **③**, the backend constructs the desired target program translating the IR into the target language representation. A compiler is often coupled with a *runtime system*, which implements the dynamic features and capabilities of the source language and controls the execution of the target program applying further optimizations.

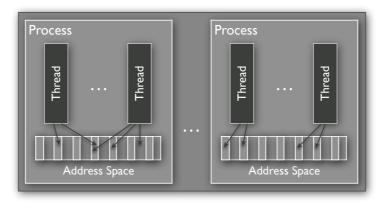

## Definition 2.14 (Process)

A *process*,  $p \in P$ , is a software entity that represents an instance of an executing program. Such an entity is composed of an address space, and one or more threads of execution.

The *address space*,  $A_p$ , represents the list of memory locations which the process p can read and write and contains program text and data, as well as other resources. These resources may include open files, signal handlers, and more. A *thread* represents a basic entity capable of processing a sequential flow of execution. Multiple threads of the same process share the same address space and consequently the

Figure 2.8: Representation of multiple process entities

same resources. Each physical or logical computing unit of a CPU runs only one thread at the time and quickly switches from thread to thread. A CPU thread features an attribute *state* that can transit at any time between three possible values:

- *running* currently using a computing unit.

- *ready* temporarily stopped to let another thread run.

- *blocked* waiting for some external event.

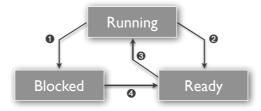

As depicted in Figure 2.9, four transitions are possible among the three values. Transition **①** occurs when the operating system discovers that a thread cannot continue. Transition **②** occurs when the operating system decides that the running thread has run long enough, and it is time to let run another thread. Transition **③** occurs when the operating system selects a thread to run. Transition **④** occurs when the the external event for which a thread was waiting happens.

Figure 2.9: Values of the attribute state of a thread

As previously describe in Section 2.1, GPUs contain computing units with a large number of execution units. Differently from CPUs, the GPU computing units are capable of executing multiple threads in parallel. Following a model known as *Single-Instruction*, *Multiple*- *Thread* (SIMT), all the individual threads running in the same computing unit (*thread group*) start at the same program address and execute in lock-step the same instructions. If some of these threads diverge via a data-dependent conditional branch, the computing unit serially executes each branch path taken, disabling the threads that are not on that path, and when all paths complete, the threads converge back to the same execution path. The execution context (program counters, registers, etc.) for each thread group processed by a computing unit is maintained until all threads have completed the execution. A computing unit can therefore switch between different thread groups with no additional cost. Full utilization of the GPU resources is achieved when all computing units have always some instruction to issue for some thread group, or in other words, when memory latency is completely hidden.

## Definition 2.15 (Sequential/Parallel Program)

A *sequential program* is defined as a program which uses a single process with a single thread of execution. On the contrary, a *parallel program* is defined as a program which uses multiple threads of execution in one or multiple processes.

Sharing the same address space, multiple threads of the same process can communicate by accessing or updating the common memory resources. This communication mechanism requires the use of synchronization constructs to coordinate the execution of multiple threads and allow exclusive access to share data. Differently, in case of multiple processes, the communication is done by message passing that allows to exchange data by sending and receiving explicit messages between processes. A formal description of this model will be presented in Section 2.4. Definition 2.16 (Speedup and Efficiency)

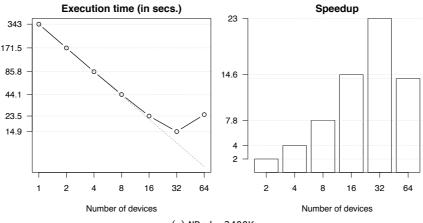

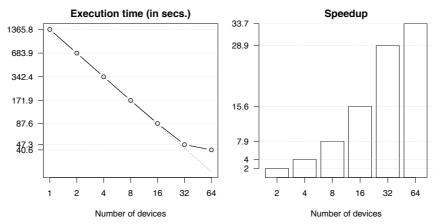

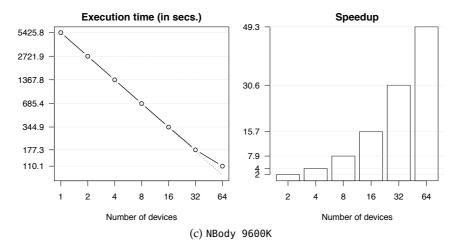

$S_n = T_s/T_n$   $E_n = S_n/n$

Let  $T_s$  be the execution time of a sequential program, and  $T_n$  be the execution time of the parallel version of the same program using n processing entities (e.g., threads, processes, compute nodes). The *speedup*,  $S_n$ , is then defined as the relation between the sequential and the parallel execution times, while the *efficiency*,  $E_n$ , is defined as the relation between the speedup and the number of processing entities.

The *scalability* of a parallel program describes how its execution time varies with the number of processing entities n. There are two distinct scalability measurement: *strong scaling* and *weak scaling*. In case of strong scaling, the number of processing entities are increased, while maintaining a constant problem size. A program is considered to scale linearly if the speedup remains close to the *ideal speedup*, which is obtained when  $S_n = n$ . In case of weak scaling, the problem size increases with the number of processing entities. A program is considered to scale linearly if the execution time stays constant while the workload is increased. In general, it is harder to achieve good strong-scaling with a large amount of processing entities since the communication overhead for many algorithms increases in proportion to the number of entities used.

## 2.3 THE OPEN COMPUTING LANGUAGE MODEL

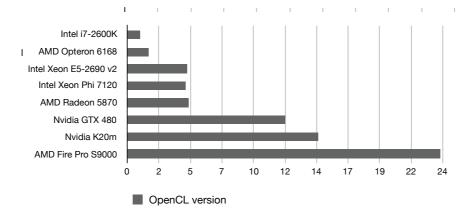

The Open Computing Language, *OpenCL* [60], is the first open industry standard for programming heterogeneous compute nodes composed of devices with different capabilities such as CPUs, GPUs, and accelerators. In the past few years, OpenCL has emerged as the de facto standard for heterogeneous computing, with the support of many industry vendors such as Adapteva, Altera, AMD, Apple, ARM, Intel, Imagination Technologies, NVIDIA, Qualcomm, Vivante, and Xilinx. In the next sections we will introduce the basic concepts and the architecture of OpenCL, followed by a detailed description of its execution and memory models.

## 2.3.1 Platform Model

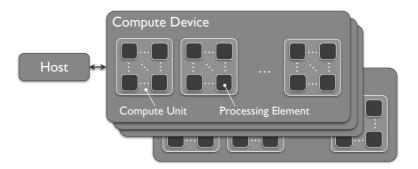

OpenCL views heterogeneous computing entities through an abstract, hierarchical *platform model*. As depicted in Figure 2.10, this model consists of a *host* connected to a set of *compute devices*.

## Definition 2.17 (Host)

A *host*, is defined as a software abstraction of the hardware entity that starts the execution of the OpenCL program. In a compute node the host is always identified with the CPU.

## Definition 2.18 (Compute Device)

A *compute device* is defined as a software abstraction of a device hardware entity such a CPU, GPU or ACL. Each compute device is composed of one or more *compute units*, and each compute unit is composed of one or more *processing elements*.

A compute node with multiple vendor compute devices features multiple vendor platforms. OpenCL offers an API to discover the set of vendor platforms and query the specific available devices. The relationship between the elements of a compute device and the components of the respective hardware entity depends on how the platform compiler optimizes the OpenCL source code, to best utilize the available physical resources. Consequently, every industry vendor offers a customized compiler that generates device-specific executable code and a runtime system capable of optimizing the execution of such code.

Figure 2.10: OpenCL Platform Model

## 2.3.2 Execution Model

An OpenCL application consists of a *host program*, executed on the host, and one or more *kernels*, executed on the compute devices.

## Definition 2.19 (Host Program)

The *host program* is the part of the OpenCL program that coordinates the execution by setting up the OpenCL environment, transferring data to and from the available compute devices and invoking the execution of the kernels.

#### Definition 2.20 (Kernel)

A *kernel* is a special function of an OpenCL program that can be executed on a compute device.

To enable host-device interaction, during the creation of the OpenCL environment, a *command-queue* is associated with each compute device. The command-queue is then used by the host program to coordinate the program execution using different types of commands:

- *kernel execution commands* to enqueue a kernel for execution on a device.

- *memory commands* to transfer data between the host and device memory.

- *synchronization commands* to constrain the order of execution of commands.

When a kernel is executed, based on a n-dimensional index space (*NDRange*), a certain number of kernel instances are created and run in parallel across multiple processing elements. Each instance, called *work-item*, is identified by a global ID that represents its position in the index space. The index space can also be subdivided into equally sized *work-groups*, each of them consisting of many work-items. Work-items can only communicate and synchronize locally, within a work-group, providing flexible scheduling options to the runtime system during the program execution. To request the execution of a specific kernel from a compute device, the OpenCL API offers a function defined as

EnqueueKernel (queue, kernel, work\_dim, global\_size, local\_size)

### where

- queue denotes the command-queue of the target device.

- *kernel* identifies the kernel to be executed.

- *work\_dim* is the number of dimensions of the index space.

- global\_size denotes the number of work-items in each dimension of the index space.

- *local\_size* specifies the number of work-items in each dimension of the workgroups.

The programming language used to express the computation inside the kernel functions is called *OpenCL C* and it is derived from the ISO C99 specification. On the one hand, to ensure hardware portability, some of the C99 features such as recursive functions, function pointers and bit fields were removed in the kernel language specification. On the other hand, OpenCL C provides several beneficial features such as support for vector intrinsics and vector data types, atomic operations and a large set of optimized built-in functions.

The OpenCL specification also defines two different profiles: a profile for compute devices (*Full Profile*) and a profile for embedded compute devices (*Embedded Profile*). Embedded devices present in SoCs have significant area and power constraints that require a relaxation in the requirements defined by the Full Profile specification. The Embedded Profile relaxes the floating-point precision requirements and support for mathematical functions, does not require atomic functions and reduces some of the minimum parameters of different components of the framework.

#### 2.3.3 Memory Model

The OpenCL memory model describes the structure and behavior of the memory exposed by an OpenCL platform during the program execution. Memory in OpenCL is divided into two parts: *host memory*, available to the host, and *device memory*, available to kernels executing on the compute devices. As depicted in Figure 2.11, the device memory comprises four memory regions:

- *global memory* largest memory space available to the device, visible to all work-items.

- constant memory read-only region of global memory.

- *local memory* memory local to a work-group, to share data between work-items in a work-group.

- private memory memory private to a work-item.

| Compute Device                                    |     |                                       |  |  |  |  |  |  |  |

|---------------------------------------------------|-----|---------------------------------------|--|--|--|--|--|--|--|

| Work-item<br>Private Work-item<br>Private Private |     | Work-item Work-item Work-item Private |  |  |  |  |  |  |  |

| Local                                             | ••• | Local                                 |  |  |  |  |  |  |  |

| Work-group                                        |     | Work-group                            |  |  |  |  |  |  |  |

| Constant Global                                   |     |                                       |  |  |  |  |  |  |  |

Figure 2.11: Device Memory regions

To provide good scalability, OpenCL offers a relaxed consistency model in which, as the computation progresses, different work-items may see a different view of global memory. Within a work-item, reads and writes to all memory spaces are consistently ordered, but between work-items, synchronization is necessary in order to ensure consistency.

#### Definition 2.21 (Buffer)

A *buffer* is defined as an OpenCL memory object that stores a onedimensional collection of data elements. Elements of a buffer can have a scalar data type (e.g., int, float), a vector data type (e.g., float4, double8), or a structure data type composed of scalar or vector data types.

Buffers are used to exchange data between host and compute devices and are passed as arguments to the kernels. The interaction between the host memory and the device memory can occur by explicitly copying buffer data between the two memory regions, or by allowing the host to map/unmap a region of the buffer into its own address space.

### 2.3.4 Programming Model

To effectively allow the mapping of parallel algorithms, OpenCL supports two different programming models: task parallel and data parallel.

## Definition 2.22 (Task Parallel Programming Model)

In a *task-parallel programming model*, problems are decomposed in tasks that can be executed in parallel on the available hardware resources.

In OpenCL to execute a program composed of multiple kernels, the host program can asynchronously push many commands in different command-queues without waiting for their completion. Each command can generate an event and be associated with a list of events that specifies dependencies on other commands. The set of commands and their respective dependencies define a task graph that the OpenCL runtime system will schedule during the program execution.

## Definition 2.23 (Data Parallel Programming Model)

In a *data-parallel programming model*, problems are decomposed in collections of data elements that can be updated in parallel applying the same stream of instructions to each data element.

This data-centric model matches perfectly the OpenCL execution model in which work-items, defined in the index space, execute in parallel the sequence of instructions specified in the kernel.

## 2.4 THE MESSAGE PASSING MODEL

The OpenCL programming model is a complete solution for programming heterogeneous compute nodes but it can not be used for internode communications in distributed memory systems. Although in some particular distributed memory system the physically separate memories can be addressed as one logically shared address space (distributed shared memory system), in this thesis we will refer only to distributed systems that rely on the message passing model to transfer data between processes. In this model, processes from different compute nodes communicate through the exchange of messages. The Message-Passing Interface, *MPI* [83], is the de facto message-passing standard for parallel processing. The technical specification of the standard is nowadays implemented in multiple libraries (e.g., Open-MPI [90], MPICH [84], MVAPICH [85]). In the next sections we will introduce the formal model of the communication protocol.

#### 2.4.1 Point-to-Point Communication Model

In the message passing model data is moved from the address space of one process to that of another process. This procedure is accomplished through the cooperation of the two processes involved in the communication. The process responsible for sending the data is called *sender*, while the one responsible to receive the data is called *receiver*. Below, we formally describe multiple functions that the model offers to allow collaborative point-to-point communications between processes. In each function we denote with P the set of all processes of a parallel program.

## Definition 2.24 (Send/Receive)

The function *send*(addr<sub>s</sub>, *size*,  $p_d$ ) specifies that a sender  $p_s \in P$  transfers *size* bytes of data from the address addr<sub>s</sub>  $\in A_{p_s}$  to a destination process  $p_d \in P$ .

The function *receive*(addr<sub>d</sub>, *size*, p<sub>s</sub>) specifies that a receiver  $p_d \in P$  receives *size* bytes of data from the process  $p_s \in P$  and stores them starting from the address  $addr_d \in A_{p_d}$ .

It is worth noting the asymmetry between send and receive functions: a receiver may accept messages from an arbitrary sender, on the other hand, a sender must specify a unique receiver. To allow the receiver to accept a message from any source process  $p \in P$  a wildcard \* can be specified as a parameter in the receive function.

Send and receive are blocking primitives. A send operation can be started whether or not a matching receive function in a remote process is called. However, the send will return only when a receive will be invoked and the data transfer will be completed. Better performance is often achievable with the use of nonblocking communication primitives. Definition 2.25 (Isend/Ireceive)

The functions *isend*( $addr_s$ , *size*,  $p_d$ , rq) and *ireceive*( $addr_d$ , *size*,  $p_s$ , rq), differently from the blocking version defined in Def. 2.24, need an additional request parameter rq used to query the status of the of the asynchronous data transfer.

The isend and ireceive functions start respectively the send and the receive operations on the data, but return immediately without waiting for a matching operation. This allows the program to proceed with the computation while the communication is taking place. During the data transfer, the sender must not modify the memory locations  $[addr_s, addr_s + size) \in A_{p_s}$ , while the receiver must not access the memory locations  $[addr_d, addr_d + size) \in A_{p_d}$ . To check for the completion of nonblocking operations the model offers two functions: *test* and *wait*.

## Definition 2.26 (Test/Wait)

The function *test*(rq, flag) sets the flag parameter to true if the operation identified by the request parameter rq is completed. The function sets the flag parameter to false otherwise.

The function *wait*(rq) returns when the operation identified by the request parameter rq is completed.

### 2.4.2 Collective Communication Model

In addition to point-to-point communications, the message passing model also defines communications that involve groups of processes. In our model, we assume that all the processes of a parallel program participate in collective communications. Below, we formally describe multiple functions that the model offers to allow such communications.

#### **Definition 2.27** (Broadcast)

The function *broadcast*(addr, *size*,  $p_r$ ) specifies that the root process  $p_r \in P$  transfers *size* bytes of data from the address  $addr_r \in A_{p_r}$  to the processes  $P - p_r$ . All the processes need to call the broad-cast function with the same root process  $p_r \in P$ , but specifying a different local destination address  $addr_d$  such that  $\forall p_d \in (P - p_r) \exists addr_d \mid addr_d \in A_{p_d}$ .

It is worth noting that while for the root process the broadcast represents a read operation, for all the remaining processes it represents a write operation in their local address spaces.

## Definition 2.28 (Scatter)

The function *scatter*(addr, *size*,  $p_r$ ) specifies that the root process  $p_r \in P$  distributes *size* bytes of data from the address  $addr_r \in A_{p_r}$  to the processes  $P - p_r$ . The outcome of the function is described by the following formula:

$\forall p_d \in (P - p_r) \exists addr_d \in A_{p_d} \mid [addr_d, addr_d + (size/|P|)) = \\ [addr_r + (size/|P|) * id_{p_d}, addr_r + (size/|P|) * (id_{p_d} + 1))$

## Definition 2.29 (Gather)

The function *gather*(addr, *size*,  $p_r$ ) specifies that the root process  $p_r \in P$  receives (*size*/|P|) bytes of data from each process  $p_s \in (P - p_r)$  and stores them starting from the address  $addr_r \in A_{p_r}$ . The outcome of the function is described by the following formula:

$$\begin{split} \forall \ p_s \in (P - p_r) \exists \ addr_s \in A_{p_s} \mid [addr_r + (size/|P|) * id_{p_s}, \\ addr_r + (size/|P|) * (id_{p_s} + 1)) = [addr_s, addr_s + (size/|P|)) \end{split}$$

## Definition 2.30 (Barrier)

The function *barrier()* blocks each caller process until all other processes have reached the same barrier.

The barrier function is only used for synchronization purposes and does not exchange any data between the processes.

# ENERGY EFFICIENT HPC ON EMBEDDED SOCS

In order to improve energy efficiency, academia and industry have been studying the suitability of low-power embedded technologies for high performance computing. Although state-of-the art embedded SoCs include GPUs that could deliver significant performance and energy improvements, until now, the HPC capabilities of such components have not been examined.

This chapter explores whether embedded GPUs can provide energy and performance advantages over the embedded CPUs, and emphasizes the importance of OpenCL software optimizations.

In Section 3.2 we provide an overview of related work. Section 3.3 describes the ARM Mali T-604 GPU Architecture followed by the OpenCL optimization techniques. In Section 3.4 we evaluate and present the results of our experiments. Finally, Section 3.5 summarizes and concludes our findings.

### 3.1 INTRODUCTION

The high performance computing community has recognized GPUs as powerful parallel computing entities, well suited for computationally demanding applications with extensive data-level parallelism [69]. A broad range of computational algorithms from different HPC domains have been successfully ported to GPUs, and heterogeneous clusters have shown distinct performance and energy-efficiency improvements over their homogeneous counterparts [15, 44].

On the other hand, in order to improve energy efficiency, the community has been deploying large-scale HPC clusters using SoCs [100, 36, 51, 52, 82, 81]. Although state-of-the-art SoCs do integrate GPUs that could provide significant improvements in terms of performance and energy efficiency, up to now, the embedded GPUs have not been used for high performance computing. The main reason behind this is that the GPUs integrated in SoCs did not support parallel programming models such as OpenCL or CUDA, and neither did they support 64-bit floating-point precision.

Nowadays the situation is changing, and the latest embedded GPUs satisfy 64-bit floating-point arithmetic precision constraints, and support computational languages such as OpenCL or CUDA [80, 114, 96]. Aware of this upcoming trend, we analyze the use of the ARM Mali GPU Compute Architecture for HPC workloads. The contributions which will be presented in this chapter are as follows:

- First, we investigated the possibility of using embedded GPUs for high performance computing. We successfully ported nine HPC benchmarks to OpenCL and executed them on ARM Mali-T604 GPU [80] the first embedded GPU with OpenCL Full Profile support. We evaluated performance, power consumption and energy-to-solution of the benchmarks and compared the results with an embedded CPU composed of ARM Cortex-A15 cores.

- Second, we identified the important OpenCL software optimization techniques for efficient utilization of the ARM Mali GPU Compute Architecture. This architecture differs in many aspects from high-end GPU architectures and OpenCL code must be optimized taking into account the particular characteristics of the underlying hardware.

- Finally, we deployed the proposed Mali GPU optimization techniques on nine HPC benchmarks and we evaluated the impact of the optimization techniques on system performance and energy consumption.

# 3.2 RELATED WORK

Recently, embedded GPU computing has drawn a lot of attention from the research community and the industry. In the embedded world, the primary graphics programming interface is OpenGL ES [61]. OpenGL ES is a subset of the well-known OpenGL 3D graphics application programming interface (API). Unlike the standard used in desktop systems and gaming consoles the Embedded Systems version removes some of the functionalities and at the same time extends it to better support the computational abilities of embedded GPUs. Although the OpenGL ES API is mainly designed for graphics, some recent studies have successfully investigated the acceleration of algorithms in embedded devices.

Singhal et al. [109, 110] explored the implementation, optimization, and evaluation of image processing and computer vision algorithms. Cheng et al. [25] investigated the computing power and energy consumption of an embedded CPU-GPU platform for computer vision applications. Lopez et al. [74] presented the first embedded GPU implementation of Local Binary Pattern feature extraction. Rister et al. [102] implemented an efficient implementation of the Scale-Invariant Feature Transform (SIFT) feature detection algorithm. Due to the difficulty in mapping algorithms to graphics operations and accessing the unexposed low-level hardware characteristics, all the previously mentioned works are specific to the field of image analysis and processing, leaving out a wide range of possible applications.

With the growth of the Open Computing Language (OpenCL) [60] as an open standard for general-purpose parallel programming of heterogeneous compute node, also the embedded community has become interested in simplified models for embedded GPU computing. Leskelä et al. [70] created a programming environment based on the standard OpenCL Embedded Profile and tested their embedded CPU-GPU backends implementation against an image processing workload. Wang et al. [122] studied the performance of an exemplar-based inpainting algorithm on the Qualcomm Snapdragon S4 chipset which supports the OpenCL Embedded Profile for both CPU and GPU [97]. Although these studies are using OpenCL, they are still restricted to the image processing area and do not investigate whether non-graphics workloads may benefit from embedded GPUs usage.

Other works have investigated how to simulate and evaluate GPUs present in embedded devices. TEAPOT [8] provides full-system cycleaccurate GPU simulation and power model for embedded workloads. The system has been used to analyze techniques that trade image quality for energy saving [8], exploit similarity between consecutive frames to save memory bandwidth [7] and hide memory latency using a decoupled access/execute paradigm [6]. Maghazeh et al. [77] investigated if a heterogeneous embedded platform with GPUs and CPUs can be an attractive solution for different kinds of applications. They implemented five benchmarks from different application domains and performed experiments on an i.MX6 Sabre Lite development board with OpenCL Embedded Profile support.

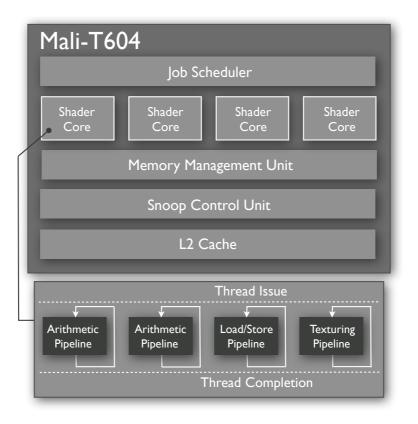

# 3.3 ARM MALI T-604 GPU ARCHITECTURE

While the main focus of embedded GPUs is mobile 2D and 3D highquality graphics, both industry and academia are becoming interested in the general purpose compute capabilities of such devices. The first effort in this direction from ARM Holdings is the Mali-T600 GPU Midgard series. The Mali GPU Compute Architecture is designed to fully comply with the OpenCL Full Profile which has strict requirements for precision and support for mathematical functions. The first GPU based on this architecture is the Mali-T604 [80]. In addition to satisfying IEEE-754-2008 precision requirements for single and double-precision floating point, Mali-T604 natively supports 64bit integer data types and implements barriers and atomics in hardware.

Figure 3.1 depicts the architectural details of the Mali-T604 GPU. The GPU supports up to four shader cores with two arithmetic pipes per core. The *Job Scheduler*, implemented in hardware, abstracts the GPU core configuration from the driver and distributes the computational tasks to maximize the GPU resource utilization. The *Memory Management Unit* can easily map memory from the CPU's address space into the GPU's address space to quickly copy or share information. The level 2 cache is shared between the shader cores and maintained coherent by the *Snoop Control Unit*.

# 3.3.1 OpenCL Optimizations for Mali GPU

OpenCL is a well designed language that allows access to the compute power of heterogeneous devices from a single multi-platform source code. Although the portability at code level ensures the execution of programs in all the devices that support the language, the same portability is not present from a performance perspective [120]. Currently, the ARM Mali GPU Architecture, as depicted in Figure 3.1, differs in many aspects from the high-end GPU architectures used

Figure 3.1: ARM Mali-T604 GPU Architecture

in desktops and servers. Under this consideration, the OpenCL code must be optimized taking into account the particular characteristics of the hardware.

Below we analyze and explain the OpenCL software optimization techniques that enable the ARM compiler to efficiently map the program to the specific ARM Mali GPU Compute Architecture.

**Memory allocation and mapping.** OpenCL is typically executed in desktop and server systems where the application processor and the GPU have separate memories and copy operations have to be used to exchange data between the host and the device. Differently, the Mali GPU Architecture provides a unified memory system where traditional copy operations are not required. Although from a hardware point of view, time and power consuming data transfers can be avoided, the Mali GPU cannot access memory buffers created with the standard *malloc* function because they are not mapped into the GPU memory space. To allow the GPU to access the data, OpenCL buffer objects have to be created using the *CreateBuffer* function with the *CL\_MEM\_USE\_HOST\_PTR* flag and data has to be copied by the host processor with the *EnqueueWriteBuffer* and *EnqueueReadBuffer* OpenCL functions. Although this method enables data exchange between host and device, it does not solve the additional copy issue. To eliminate all the computationally expensive copies it is necessary to allocate the memory through the OpenCL API and to use memory mapping functions. Buffers have to be allocated using the *Create-Buffer* function with the *CL\_MEM\_ALLOC\_HOST\_PTR* flag and the *EnqueueMapBuffer* and *EnqueueUnmapMemObject* have to be used to enable both the application processor and the Mali GPU to access the data.

**Load distribution.** Another important aspect of an OpenCL program is the load distribution between the processing elements of a device. As already described in Section 2.3.2, the API offers a function called *EnqueueKernel* to execute a kernel on a device. To allow control over the load distribution some arguments of the function describe the dimensionality of the data, the number of work-items to be processed for each dimension (*global\_size*) and the number of work-items in a work-group for each dimension (*local\_size*).

As suggested in the official Mali OpenCL Developer Guide [79] the optimal *global\_size* can be calculated as the device *maximum\_work-group\_size* multiplied by the number of shader cores multiplied by a constant. This constant for the Mali-T604 is four or eight. More generally, the *global\_size* must be in the order of several thousand to maximize the GPU resources utilization and to achieve high performance. With regard to the local work-group size, if the application is not required to share data among work-items, the Developer Guide [79] suggests to set the *local\_size* parameter to NULL and let the OpenCL driver determine the most efficient *work-group\_size* for the kernel. Although this practice simplifies the selection of the *work-group\_size* value, during our experimental evaluation we noticed some performance degradation and we strongly suggest to manually tune the *local\_size* parameter.

Memory Spaces. Defined as a generic language for heterogeneous computing, OpenCL exposes a memory model composed of several memory spaces that every vendor maps differently to the corresponding available hardware. Usually dedicated GPUs present local memories with much higher bandwidth and lower latency than the GPU memory unit. The OpenCL implementations offered by the two vendors map the local memory space to the local memories making the exploitation of locality at code level one of the most important factors in achieving high performance. Differently, Mali GPUs have a unified memory system where local memory is physically mapped to the global memory. For this reason, traditional code locality optimizations are not required, simplifying the coding of optimized OpenCL kernels.

Thread Divergence. Other optimizations usually used in GPU computing are those regarding warp or wavefront execution. Warps or wavefronts represent the smallest executable units of parallelism on NVIDIA or AMD devices (respectively 32 or 64 work-items). This means that if two work-items inside a warp or a wavefront take divergent paths of the control flow, all work-items of the same unit go through both paths. This issue is called thread divergence and can significantly affect the instruction throughput of the computational kernel. The thread divergence problem is not present in the ARM Mali GPU Architecture because the smallest unit of parallelism is a single thread (work-item) that, being independent, cannot diverge.

**Vectorization.** One of the most important hardware characteristic to take into account during the development of OpenCL code for the ARM Mali GPU Architecture is that the shader cores contain 128-bit wide vector registers. To allow the effective programming of such units, OpenCL offers vector load and store instructions and vector types of different sizes. Vectorization of an OpenCL scalar code can be done by converting the scalar data types (e.g. float) to vector data type (e.g. float4) increasing the number of elements processed by each work-item and consequently reducing the *global\_size* in the host code. This optimization not only promotes the use of hardware resources, but also allows a reduction of the run-time scheduling overheads due to the decrease in the number of work-groups.

**Vector Sizes.** OpenCL, as already mentioned, provides vector types of different sizes that the compiler must map to the corresponding hardware vector registers. In case of the ARM Mali-T604, we noticed that, after vectorizing the kernel, the best achievable performance is not bound to a particular vector size but can vary from case to case. Using types wider than the underlying hardware can improve the instruction-level scheduling, but also increase register pressure. For this reason, we suggest, whenever the code allows it, to experiment

with different vector sizes (e.g. size of 4, 8, 16). It is also important to keep in mind that vector load and store operations access multiple data elements in memory with a single instruction leading to a more efficient use of the available bandwidth. For this reason, such operations should be also used in kernels that do not take advantage of vector registers but process each element of the vector array individually.

Loop Unrolling. Another opportunity for vectorization of the kernel code is within loops. A loop can be unrolled and multiple instructions can be replaced with a single vector instruction which operates on multiple data elements. Although this optimization usually leads to performance improvements on relatively long loops, in case the number of iterations is not a perfect multiple of the vector size, the overhead due to the correct handling of the last iterations of the loop has to be considered. The best performance for different kernel codes can be achieved using vectorization and unrolling, taking into consideration that code replication can also lead to performance degradation.

**Data Organization.** In vector architectures, the organization of data is of primary importance. Typically in application code data is packed in an Array of Structures (AOS). If we consider a set of three dimensional points, their representation would be an array in which each element is a structure with *x*, *y*, *z* coordinates. Although this representation is the most natural, it typically requires multiple load/shuffle/insert or gather instructions to correctly populate the vector registers. A more efficient data-packing approach is Structure Of Arrays (SOA). In this representation, the data types are the same across the vector. With this approach, the list of points would be organized as three arrays containing respectively the *x*, *y* and *z* values that would facilitate the application of vector instructions increasing the code performance.

**Directives and Type Qualifiers.** Better performance can also be achieved by passing additional information to the OpenCL compiler through the use of directives and type qualifiers. With function inlining the user can increase the size of basic blocks (sequences of consecutive instructions without branches) and eliminate the overhead associated with the function call. The use of the *const* keyword in pointer declarations makes possible to declare pointers to constant

data and allows the compiler to make more assumptions and therefore produce significant optimizations. The restrict qualifier, applicable to the arguments of a kernel, enables the compiler to assume that the pointer is the only way to access the object to which it points, limiting the effects of pointer aliasing.

# 3.4 EVALUATION

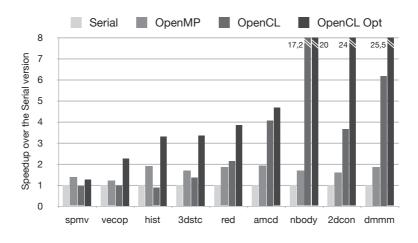

In order to evaluate the Mali-T604 GPU and the OpenCL optimizations techniques presented in Section 3.3.1, we used a set of nine HPC benchmarks. These benchmarks cover a wide range of algorithms employed in HPC applications and stress various architectural features. They have been already used in previous studies [99, 101] to evaluate the suitability of embedded platforms for HPC systems. Below, we briefly describe each of the benchmarks.

**Sparse Vector-Matrix Multiplication (spvm)** benchmark multiplies a vector and a sparse matrix to produce a new vector. It is useful as metric to measure performance in cases of load imbalance.

**Vector Operation (vecop)** benchmark performs an addition of two vectors in an element-by-element basis. Given the memory-bound nature of the kernel, this benchmark stresses the memory bandwidth of the platform under study.

**Histogram (hist)** benchmark computes the histogram of the values present in a vector using a configurable bucket size. It uses local privatization that requires a reduction stage which can become a bottleneck on highly parallel architectures.

**3D Stencil (3dstc)** benchmark produces a new 3D volume from an input 3D volume. Each point of the output is a linear combination of the point with the same coordinates in the input and the neighboring points on each dimension. This benchmark is useful to evaluate the performance in presence of memory accesses with regular strides.

**Reduction (red)** benchmark applies the addition operator to produce a single (scalar) output value from an input vector. Reduction is a common operation in many computational kernels and allows to measure the capability of the compute accelerator to adapt from massively parallel computation stages to almost sequential execution. Atomic Monte-Carlo Dynamics (amcd) benchmark performs a number of independent simulations using the Markov Chain Monte Carlo method. Initial atom coordinates are provided and a number of randomly chosen displacements are applied to randomly selected atoms which are accepted or rejected using the Metropolis method.

**N-Body (nbody)** benchmark takes as input, a list of bodies described with a set of parameters (position, mass, initial velocity) and updates their information after a given simulated time period based on gravitational interference between each body.

**2D Convolution (2dcon)** benchmark produces a new matrix from an input matrix of the same size. Each point of the output is a linear combination of the point with the same coordinates in the input and the neighboring points. Differently from the 3D stencil computation, neighboring points can include points with the same coordinates as the input point plus/minus an offset in one or two dimensions. This benchmark is useful to evaluate the performance in presence of spatial locality and strided memory accesses.

**Dense matrix-matrix Multiplication (dmmm)** benchmark performs the multiplication of two dense input matrices. Matrix multiplication is a common computation in many numerical simulations and measures the ability of the compute accelerator to exploit data reuse and compute performance.

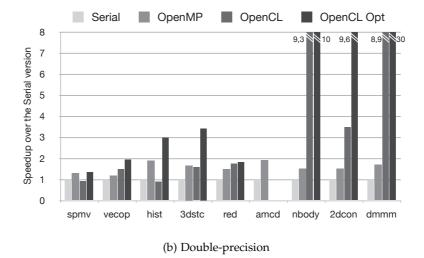

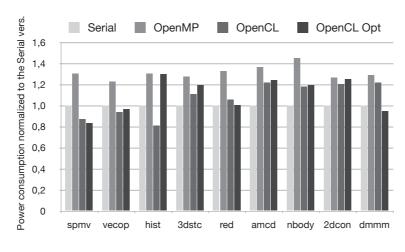

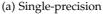

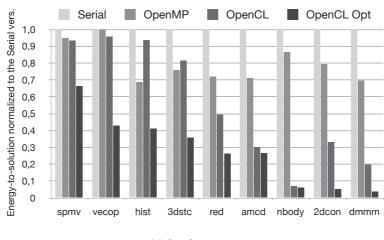

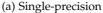

Each benchmark was implemented in four different versions: *Serial*, *OpenMP*, *OpenCL*, and *OpenCL Opt*. The *Serial* benchmarks were designed to execute on a single core. The *OpenMP* benchmarks, through the use of threads, were designed to execute in parallel on several CPU cores. The *Serial* and the *OpenMP* versions have been already developed and used by previous studies [99, 101] that tested the suitability of SoCs for high performance computing. These versions do not make use of vector instructions. This is due to the fact that the ARM Cortex-A15 CPU does not incorporate a double-precision SIMD unit and full IEEE-754-2008 floating-point vector support. The *OpenCL* versions of the benchmarks were developed in the Open Computing Language to allow a parallel execution on the GPU.

Recently, data structures and data layout transformations have been proposed to efficiently implement some of the algorithms used in our benchmarks [17, 73, 45]. However, in order to maintain a similar code base for all CPU and GPU implementations, we do not take advantage of them. One of the main goals of the study is to quantify the performance and energy improvements of the proposed OpenCL optimization techniques. In this regard, we enhanced the *OpenCL* benchmarks following *only* the guidelines presented in Section 3.3.1. The new versions of the benchmarks are referred to as *OpenCL Opt*.

To avoid rewriting the host code with different data transfer techniques, both, *OpenCL* and *OpenCL Opt* benchmarks make use of the host memory mapping, exploiting the unified memory system offered by the architecture. Due to the problem of data transfer already being well known in the heterogeneous computing field of research [41], we want to place more emphasis on other important optimization aspects during the comparison between the *OpenCL* and *OpenCL Opt* versions of the benchmarks.

The experiments were executed on Samsung Exynos 5 Dual Arndale Board [105]. The board comprises the Samsung Exynos 5250 embedded system-on-chip (SoC) and is equipped with 2 GB of DDR3L-1600 memory. The Samsung Exynos 5250 integrates a dual-core ARM Cortex-A15, running at 1.7 GHz with 32 KB of private L1 instruction and data cache, and 1 MB of shared L2 cache. Alongside the CPU, the SoC features a four-core ARM Mali-T604 GPU whose architecture has been already described in Section 3.3.